# Design and Implementation of Efficient 8-Bit SIPO Shift Register

# Sandeep Kakde<sup>2</sup> S, Rajesh Thakare<sup>2</sup>, Shailesh Kamble<sup>3</sup>, Umakant Mandawkar<sup>4</sup> and Swapnil Mali<sup>5</sup>

<sup>1,2</sup>Department of Electronics Engineering, Yeshwantrao Chavan College of Engineering, Nagpur, Maharashtra, India.

<sup>3</sup>Department of Computer Technology, Yeshwantrao Chavan College of Engineering, Nagpur, Maharashtra, India.

<sup>4</sup>Department of Computer Engineering, Sandip University, Nashik, India

<sup>5</sup> Department of Electronics & Telecommunication Engineering, College of Engineering, Pune, India

### D.O.I - 10.51201/12496 https://doi.org/10.51201/12496

**Abstract:** Area and power are main design constraints in analog and digital circuits. In this paper, a low-power 8-bit shift register is implemented by using true phase single clock (TSPC) D- flip flop which is based on single clock and two clocked transistors. The proposed design successfully solves the long discharge path problem which is bound to occur in conventional type of D-Flip Flop. This paper describes 8 bit serial in parallel out (SIPO) shift register using True Single-Phase Clock(TSPC) technique which reduces an area in terms of transistor count by 85.29%.

#### Keywords: Reversible Logic, Area, Power, Sequential Circuits.

#### **1. INTRODUCTION**

First shift register is built using vacuum tubes [1]. Thereby they started to minimize the area and power consumption. Today area utilization, power dissipation [2-4] becomes an important design issue in VLSI circuits .This tends to pay attention on power dissipation and number of transistors. When it comes to portability of devices, power dissipation is an unavoidable constraint [5-8]. Due to scaling of technologies, the power consumption per unit area of the chip has risen tremendously.

The main contribution of this work is to implement 8 bit SIPO shift register using True Single-Phase Clock technique. Area and power aware design is described in this paper. The schematic entry and functional verification is successfully done using DSCH tool.

Rest of the paper is arranged as follow: Section 1 highlights an introduction part. Section 2 demonstrates the existing types of shift registers. Section 3 focuses on the proposed approach .Section 4 demonstrates experimental results and section 5 concludes the paper.

#### 2. Shift Registers

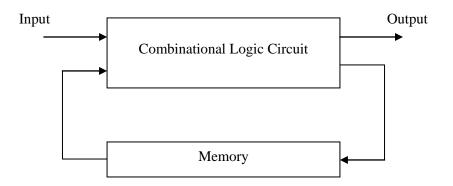

Sequential has two states. It maintains the state until receiving a trigger. Figure 1 shows the general block diagram of sequential circuits. Output depends on the present input and past outputs [9-10]. There is a memory unit to store immediate results.

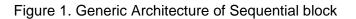

Types of Shift registers (SR) are as shown in Figure 2.

Figure 2. Types of SR

Serial In Serial Out Register:

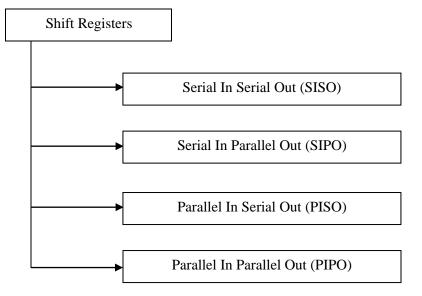

Figure 3. Typical Architecture of SISO Block

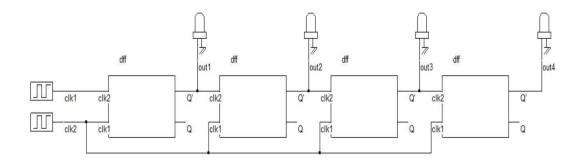

#### Serial In Parallel Out Shift Register:

It consists of serial input and gives a parallel output,[11-12]. Figure 3 shows the block diagram of SIPO register. A conventional block requires 4 D flip flops to implement 4-bit SIPO register.

Figure 4. Typical Architecture of SIPO Block

#### Parallel In Serial Out Shift Register:

This block can be implemented with four D-flip-flops, where the CLK signal is connected simultaneously to all the FFs [13-14].

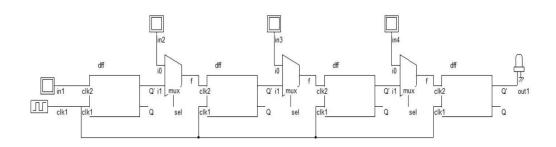

Figure 5. Typical Architecture of PISO Block

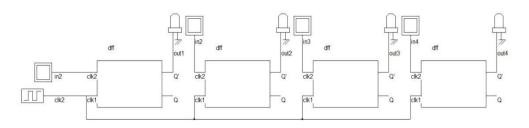

#### Parallel In Parallel Out Shift Register:

# Figure 6. Typical Architecture of PIPO Block

Here the data is given as input individually for every flip-flop [15], as well as the output is also received separately from every flip flop.

# 3. Proposed Research Method

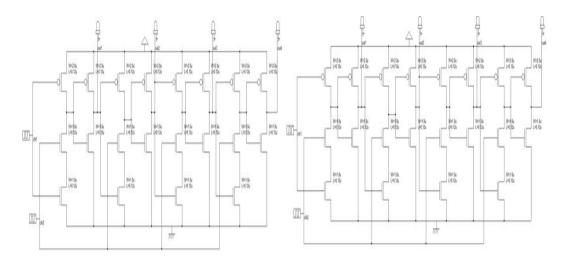

In this paper, two techniques are implemented.

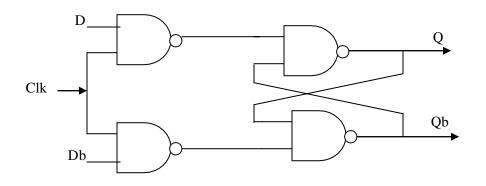

D Flip flop implemented with Latches using NAND Gates

Four NAND gates are required to implement D Latch and with cascading two latches, one Flip flop is implemented as shown in Figure 8.

Figure 7. Simple Latch

Figure 8. D Flip Flop

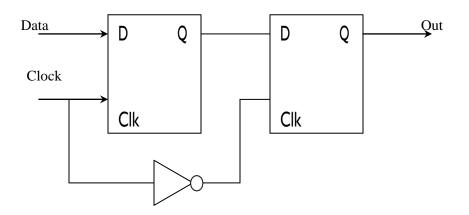

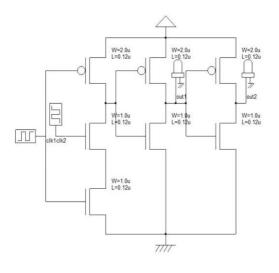

D Flip Flop implemented using True Single Phase Clock Latch (TSPC):

This circuit consists of seven transistors out of which two inverters are present. Schematic of latch is as shown in figure 9.

Figure 9. Schematic of TSPC Latch

Figure 10. Schematic of 8-bit SIPO Shift Register

# 4. Experimental Results and Discussion

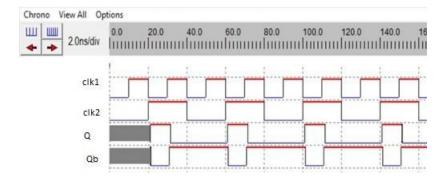

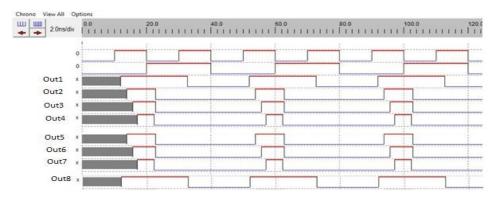

All the schematics are functionally verified by their truth tables. These waveforms are the simulation results of circuits, which are designed using electronic design automation DSCH tool. From the Table 2, it clearly shows that conventional method requires 272 transistors where as TSPC based approach required only 40 transistors. Therefore, reduction in transistor count demonstrates area optimization.

Figure 11. Timing waveforms of D-FF circuit

Figure 12. Timing waveforms of 8-bit SIPO Shift Register

Table 1: Power consumption and Area

| 8-bit SIPO shift register        | Power consumption (µW) |

|----------------------------------|------------------------|

| Conventional method (NAND LATCH) | 493.62                 |

| Proposed method (TSPC LATCH)     | 117.66                 |

Table 2: Area (in terms of transistor count) Comparison

| Techniques                       | 8-bit SIPO shift register |

|----------------------------------|---------------------------|

| Conventional method (NAND LATCH) | 272                       |

| Proposed method (TSPC LATCH)     | 40                        |

# 5. Conclusion

In this paper, low area and power efficient 8-bit serial input parallel output shift register is designed using TSPC D-FF. The properties are improved by reducing the number of transistor and minimizing the discharging path. The circuit is also very simplified unlike the convention NAND latch based SIPO. In this paper, two latch systems are described namely 1) NAND latch 2) TSPC latch. By implementing and comparing these two methods, we conclude that by enhancing and implementing good latch system, we can control area and power consumption. The conventional method which uses the NAND latch for circuit implementation requires more number of

transistor's than TSPC latch based SIPO. In NAND latch, each latch requires 4 transistors. Every D-FF requires 2 latches and one inverter which has total number of transistor count as 34. This means the fully functional 8-bit SIPO is required 272 transistors. In TSPC latch based D-FF requires only 7 transistors but as the SIPO don't require Q' output therefore it can reduced to 5 transistors and the SIPO block requires only 40 transistors. It reduces an area by 85.29 %.

#### REFERENCES

- [1] Purkayastha, Tamoghna, Debashis De, and Tanay Chattopadhyay. "Universal shift register implementation using quantum dot cellular automata." Ain Shams Engineering Journal 9, no. 2 (2018): 291-310.

- [2] Jeon, Jun-Cheol. "Low-complexity QCA universal shift register design using multiplexer and D flip-flop based on electronic correlations." The Journal of Supercomputing 76, no. 8 (2020): 6438-6452.

- [3] Das, Jadav Chandra, and Debashis De. "Operational efficiency of novel SISO shift register under thermal randomness in quantum-dot cellular automata design." Microsystem Technologies 23, no. 9 (2017): 4155-4168.

- [4] Divshali, Mojtaba Niknezhad, Abdalhossein Rezai, and Asghar Karimi. "Towards multilayer QCA SISO shift register based on efficient D-FF circuits." International Journal of Theoretical Physics 57, no. 11 (2018): 3326-3339.

- [5] Bhuiyan, Mohammad Arif Sobhan, Arvin Mahmoudbeik, Torikul Islam Badal, Mamun Bin Ibne Reaz, and Labonnah F. Rahman. "Low power D flip-flop serial in/parallel out based shift register." In 2016 International Conference on Advances in Electrical, Electronic and Systems Engineering (ICAEES), pp. 180-184. IEEE, 2016.

- [6] Li Li, Ken Choi, and Haiqing Nan, "Activity-Driven Fine-grained Clock Gating and Run Time Power Gating Integration", IEEE transactions on very large scale integration (VLSI) systems, vol. 21, no. 8, August 2013.

- [7] J.S.Wang.P.H.Yang, "A Pulse Triggered TSPC FF for High speed, Low power VLSI design Applications" IEEE, 1998

- [8] Badal, Mohammad Torikul Islam, Mamun Bin Ibne Reaz, Zinah Jalil, and Mohammad Arif Sobhan Bhuiyan. "Low power high-efficiency shift register using implicit pulse-triggered flipflop in 130 nm CMOS process for a cryptographic RFID tag." Electronics 5, no. 4 (2016): 92.

- [9] Li, Ting, and Roy Kornovich. "An Optimized Design of Serial-Input-Serial-Output (SISO) and Parallel- Input-Parallel-Output (PIPO) Shift Registers Based on Quantum Dot Cellular Automata Nanotechnology." International Journal of Theoretical Physics 58, no. 11 (2019): 3684-3693.

- [10] Padmanabhan, Ashwin, Allen Vivean Miranda, and T. Srinivas. "An efficient design of 4-bit serial input parallel output/serial output shift register in quantum-dot cellular automata." In 2016 3rd International Conference on Computing for Sustainable Global Development (INDIACom), pp. 2736-2738. IEEE, 2016.

- [11] K. Usami and N. Ohkubo, "A design approach for fine-grained run-time power gating using locally extracted sleep signals," in Proc. Int. Conf. Comput.Design, 2006, pp. 151–161

- [12] L. Bolzani, A. Calimera, A. Macii, E. Macii, and M. Poncino, "Enabling concurrent clock and power gating in an industrial design flow," in Proc.Des. Autom. Test Eur. Conf., 2009, pp. 334–339

- [13] Andrew B.Kahng, SeokhyeongKang, BongilPark, "Active-Mode Leakage Reduction with Data-Retained Power Gating" Proc EDAA, 2013

- [14] Y. Tsai, D. Duarte, N. Vijaykrishnan, and M. Irwin, "Characterization and modeling of runtime techniques for leakage power reduction," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 12, no. 11, pp. 1221–1233, Nov. 2004.

- [15] P. Babighian, L. Benini, and E. Macii, "A scalable algorithm for RTL insertion of gated clocks based on ODCs computation," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 24, no. 1, pp. 29–42, Jan. 2005.

- [16] K. Roy, S. Mukhopadkyay, and H. Mahmoodi- meimand, "Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOScircuits," Proc. IEEE, vol. 91, no. 2, pp. 305–327, Feb. 2003.

- [17] Neil H.E Weste, Kamran Eshraghian, "Principles of CMOS VLSI Design," A Systems Perspective, Second Edition, Pearson Education Inc ,2002