## ANALYSIS OF LOW POWER AND HIGH SPEED DOUBLE TAIL COMPARATOR USING GNRFET TECHNOLOGY

## Vineet Dubey<sup>1</sup>, Dr. Imran<sup>2</sup>

<sup>1</sup>M.Tech.(EE) Scholar, Electrical Engineering department, Azad Institute of Engineering & Technology Lucknow, India

<sup>2</sup>Assistant Professor, Electrical Engineering department, Azad Institute of Engineering & Technology Lucknow, India

<sup>1</sup>Email-vineetd9@gmail.com

<sup>2</sup>Email-pe.imran@gmail.com

**Abstract:** Moore's guideline has been a fundamental benchmark for patterns in the locale of microelectronics and measurements preparing. It has played an instrumental position in driving the part financial aspects and downsizing of the component time frame has been the major system for improving the general execution of the gadget. in any case, as we hold to diminish, close to the nanometre routine, various elements like line region unpleasantness, burrowing outcomes, arbitrary dopant changes, fast channel results and numerous others has a tendency to impact it's working and there upon, it's rise as of intense quintessence to investigate other open door substances that may help intensify the soaking Moore's guideline. some of research is as of now going inside the zone and numerous open door advances like CNFETs, FINFETs, GNRFETs. Region sway transistors the utilization of Graphene Nano-Ribbons (GNRFETs) has developed as promising innovation as a result of their stunning supplier transport homes and capacity for huge scale preparing and creation. This paper investigates the GNRFETs inverter generally speaking execution with CMOS inverter at 32nm time hub. Reproductions recommend about 2.5x upgrades inside the proliferation dispense with and 2x enhancements inside the quality put off item (PDP). what's more improvement of results was gotten through different the kind of Nano-Ribbons together with the convey voltage. On different the broad kind of nano-ribbons it have turned out to be set that, spread put off reductions, at the indistinguishable time as powerful power utilization will increment. principally based definitely at the derivation, the upgraded outcome altered into chose to be 15 nano-ribbon. The outcomes imply that that GNRFET is a promising open door for Si-CMOS, making it a splendid recommendation to help intensify the soaking Moore's law. Graphene is an exciting new fabric with radiant electric properties, for the most part inside the state of graphene nanoribbons. on this educational document, we inspect steel-oxide-semiconductor and graphene nanoribbon discipline- impact transistors and recommend the proceeded with utilization of MOSFETs through 2023. This archive fills in as top notch initial texture for people with a legacy in semiconductors who want to find out about graphene and GNRFETs.

Keywords: Microelectronics and measurements preparing, Nanometre routine, Graphene nanoribbons, Steeloxide-semiconductor, Transistors

## **1. INTRODUCTION**

The Low-Power Double Tail Comparator is concentrated in this proposition. The low control, regionally skilled, and fast to-advanced easy to-converters demand focuses on using renewable dynamics to extend velocity and energy productivity These low speed dynamic regenerative comparators are used in low power and regionally computerized converters that are simple to use in order to improve speed and energy efficiency. The two factors that define the precision of the

comparator are speed and power use. The comparator structure can be changed more quickly and progressively. This further reduces the power consumption and increases the velocity by reducing the loop delay. Electronic equipment, for instance, is used in all constructions, transport and recreational apps, in the families, etc. Every now and then in different areas. The condition for easy to sophisticated converters is to step by stage expand as they suppose a remarkable task in altering to computerized models via the easy symbol."The ADCs interface the characteristic simple world with the ever-changing computerized world. The main circle that is the ADC's concentrate is the Comparator. A comparator is usually defined as an electronic gadget that contrasts the simple sign and reference voltage given and produces a progressive output i.e. rational outcome '0' or rational '1. 'Should the contribution offered to the non-altering information be more remarkable than the reorganizing input, the return is a legitimate 1.If the contribution to the non-modifying information is not so much the contribution to the transforming output, the return is a consistent 0.

The comparator is one of the most critical basic structures in easy and mixed mode circuits. A CMOS comparator has the main ability to compare an data message and a comparison mark and to produce a combined symbol output. A low-counter balance of the low-control use small area comparator is a important loop obstruction for certain apps, such as storage detect circuits, easy to sophisticated converters. For some apps, compare components use successive inter paired inverters for sophisticated output over that specified voltage. A dynamically closed comparator is more flexible than the usual static linked comparator. The increase of two inverters in the regenerative hook phase between the information and return phase of the conventional dual-tail vibrant comparator has been enhanced. Timed renewable comparators are pins and nozzles of the circuit boards which, because of favorable feedback, are usually received by cross-coupled inverters (locking). The prerequisite is the use of dynamically regenerating comparators to increase speed and control capability for ultra-low control, zone production and quick simple to- computer converters. The complete exam of the postponement of the dynamic benchmarks will be shown, as will the study articulation, creators can acquire an instinct on the primary supporter of the benchmark delay and look closely at exchange offs, which have occurred in a unique comparator plan[3]. In most of the simple to-advanced converters (ADCs), the comparator is one of the basic structures obstructs. Many quick ADCs, for instance, streak ADCs, involve quick, small-chip area energy comparators. The comparator is a device which combines a easy symbol with a different easy voltage or base tension and gives the difference the double signal. However, as the innovation improves the straightforward comparators can not keep pace with fast mechanical progressions so that we need low power, low area and high speed, simple to advanced converters to minimal postponement. In order to comprehend all these, vibrant regenerative comparators are necessary to enhance velocity and efficiency.

These regenerative comparators have also been altered as double head comparator and improved in low voltage apps by the faster execution of this framework. The suggested framework is implemented by means of GNRFET and a postponement study, with different science phrases the average energy and energy. The GNRFET is an increasing innovation, which has been given a decent treatment over the last few years. The GNRFET is the new transistor for graphene. The latest recreation circuits have shown that GNRFETs are also capable of having low-power programs. In this thesis, we break down the reconstruction for low-power analysis and high-speed double-decker comparator that utilizes GNRFET technology, because GNRFET has a large number of points of interest that it uses less power. Here we use GNRFET circuits that have low standard strength, postponement and vitality. In this context, we contrast the various circuits and circuits proposed, using the Comparator based on MOSFET, Proposed Comparator based on GNRFET, Proposed MOSFET and a Comparator Proposed based on GNRFET. Here, we're supposed to achieve low power, low deferment and low vitality.

#### A. MOTIVATION

The rule bit of leeway of twofold tail comparator is that they can work in lower voltage and has less stacking. This twofold tail comparator has two tails Mtail1 and Mtail2 for quicker task and lower balance and therefore its activity and execution is greatly improved utilizing the innovation of GNRFET.

Rapid gadgets were the critical destiny of these days. A remarkable center for low power procedures is also provided for these quick applications. Minimizing the intense use of these gadgets can be done by examining methods for smaller elements. Whatever happens, the procedural variations and other no idealities will affect the overall execution of the gadget whenever we progress towards small-scale processes.

Another parameter which to a great extent adds to the general execution of the circuit is limiting the postponement. By affecting two important aspects, the presented model improved the velocity of a double tail comparator. It upgrades the fundamental voltage to the beginning of the regeneration directly from the bat and also creates the convincing hook system transductance and it can be very well found that the inner beneficial critique of this GNRFET strengthens the whole lock restoration process. In this way joining the benefits of Graphene nano ribbon exhibited the much-improved outcomes.

#### **B. OBJECTIVE**

The objective of this project is to decrease average power, Delay and Energy using the GNRFET. Earlier works related to the theory of Double tail comparator using MOS, CMOS and other technologies did not reveal such wonderful result. However, for the purpose of comparison we have taken MOS and compared with the GNRFET which shown much improved version of results. However, the technology of Double tail comparator is same here but it is carried out using the properties of Graphene which has excellent advantage of Zero band Gap.

## 2. LITERATURE SURVEY

Ms. Sheik Shabeena : et.al High pace dynamic regenerative comparators are utilized in low power and area productive simple to computerized converters to improve speed and power execution. Pace and power utilization are the two components that define the comparators precision. By affecting two important aspects, the presented model improved the velocity of a double tail comparator. It upgrades the fundamental voltage to the beginning of the regeneration directly from the bat and also creates the convincing hook system transductance and it can be very well found that the inner beneficial critique of this GNRFET strengthens the whole lock restoration process.

S.Rahmani et.al., By affecting two important aspects, the presented model improved the velocity of a double tail comparator. It upgrades the fundamental voltage to the beginning of the regeneration directly from the bat and also creates the convincing hook system transductance and it can be very well found that the inner beneficial critique of this GNRFET strengthens the whole lock restoration process. Both energy dispersion and deferment moment could be significantly reduced within the suggested vibrant double nose comparator system. In both 0.18-µm and 65-nm CMOS advances, the introduced comparator is planned and mimiced.

Adi narayana Salina :et.al Comparator is one of the essential structure basic squares of simple to virtual converter. The requirement for ultra-low-control, area green and high pace simple to-

computerized converters is pushing nearer to utilizing dynamic regenerative comparators to upgrade speed and productivity of vitality. Numerous high pace ADCs, alongside blaze ADCs, require high-pace, low power comparators with little chip place. This endeavor has an assessment at the deferral of single Tail comparator, Double Tail Comparator and twofold tail comparator for low power can be as looked at hypothetically and almost.

Vaishnavi Jumade :et.al At present, the importance of comparators is considerably increased due to their use in easy to-advanced converters. The increased demand for quick comparators has gradually extended ADC's skilled duties. At present, the importance of comparators is considerably increased due to their use in easy to-advanced converters. This article presents the use of the double threshold comparator for faster ADC's operation. There are preamplifier phase and hook stages in the design of a dual head comparator. The loop design of a usual comparator is modified and combined with a double vibrant threshold comparator to reduce the energy adjustment and tension by increasing the velocity.

Yijian Ouyang: et.al., Graphene Nanoribbon FETs Scaling Comportement: A Three Dimensional Simulation Study of Quantum. The scaling of the Schottky hydraulic transistor nanoribbon (GNR) graphene is considered as an atomic assumption, which includes a three-dimensional Poisson situation, to comprehend and break down the non-balance Green's travel situation (NEGF). The GNR channel circuit on the rocker edge gives similarities to a CNT crisscross, but has an alternative basic geometry and a transverse cA multiplicity of auxiliary gate geometry improve and upgrade short channel impact resistance, however, in comparison to Si MOSFETs, it provides less improvement in terms of current and transductivity.ondition of quantum limitation. The negligible spillage power has increased critically.

Abhijith A Bharadwaj: et.al The particulars of low zone, rapid ICs are the commitment of MOSFET scaling systems. Points of confinement on MOSFET scaling results a requirement for new transistor innovation. Here it gives three SRAM (6T) cell models (Graphene Nanoribbon FET, Multi-walled CNT FET and MOSFET) which gives the route for innovation. The parameters as Read delay, write deferral and Power-postpone item are thought about. All the three innovations, 10nm gate length is taken. Plan and reproduction of a total SRAM cell is then considered (6T SRAM cell, Sense intensifier, Precharge circuit, Read and Write circuits) to give control examination between 32X8, 32X16, 64x8 and 64x16 SRAM clusters. Circuit is structured and reenactment was finished utilizing HSpice and Cosmos Scope.

Praveena Kumari: et.al 16-bit design and evaluation The Moore law is not to be revised over the extra since MOSFET can not be extended below 10 nm due to its physical and auxiliary properties. The GRNFET (Graphene Nano Ribbon Field Effect Transistor, GNRFET) is the first of the two modalities. This Trade-Off outcomes in a Way For New Material Used In Fetes To be as per Moore's Law. Different Other Technologies Include Carbon Nano-Tube FET (CNTFET), Fin-Shaped FET (Finfet), Reconfigurable Logic, Reversible Logic, And Grapheme Nano-Ribbon FET (GNRFET), Among The Available advancements GNRFET's Has Proven To Be An altogether Promising Potential Replacement In Terms Of Design Area, Faster Operation, Lower Power Consumption.

Preetika Sharma: et.al Effect of temperature on conductivity of GNRFET Graphene nano ribbons are the layers and segments of graphene sheet which has open band hole in graphene. This opening of band hole upgrades the on off proportion of GNR gadgets and add to its utilization in rationale circuit applications. GNR in transistors give long range applications in these zones. A GNRFET indicates enormous conductance with gate voltages.

HueiChaengChin: et.al Enhanced Graphene Nanoribbon Device and Circuit level benchmarking Field effect transistor to nano MOSFET with GNRFET (German Nano- MOSFET) and a nanoscale metaloxide field-impact transistor (nano MOSFET) is displayed for ultra-large scale integration applications.GNRFET in circuit design and execution is unmistakably unrivaled.GNR's extraordinary shipping features lead it to an elective development that limits silicon based gadgets.Sprouting GNRFET, utilizing the circuit level displaying programming SPICE.

Amit Sangal: et.al., GNRFET as potential low-energy gadgets The GNRFET (GNRFET) is an advancement which has taken a great deal of account as far back as recently.Late work on the reenactment of a GNRFET system shows that GNRFETs can have potential in low-power applications. In this paper, you will see the latest work on display of the GNRFET circuit, consider the two games of GNRFETs: the metal oxide semi-conducters (MOS) type, and the Schottky Barrier (SB) type GNRFETs.Our reenactments show that, in contrasts with the standard (HP) Si-CMOS and low control (LP) SiCMOS, ideal (non-ideal)MOS-GNRFET usage 18% (35%) and 54% (103%).In terms of energy usage, SB-GNRFET does not favorably compare to MOSGNRFET.In any case, the perfect (non-perfect) SB-GNRFET is separate from the Si-CMOS (HP) and the Si-CMOS (LP), whereas ideal (non-ideal) MOS-GNRFET is 8% (93%) and1.25% (14.3 percent) EDP compare individually with Si-CMOS (HP) and Si-CMOS(LP).

## **3. VOLTAGE COMPARATOR**

High pace dynamic regenerative comparators are used in low power and area proficient simple to computerized converters to improve pace and power effectiveness. pace and quality utilization are the two factors that define the comparators exactness. A comparator is a gadget that believes of two voltages or streams and gives a larger digital symbol. Another double tail comparator for the energy blue and high-speed operation has been suggested on this document with techniques for altering the low voltage double tail comparator loop. Each power dissemination and off time can be significantly reduced in the proposed dynamic double tail comparator gadget.

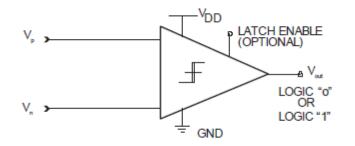

Figure 3.1: Comparator showing outputs 0 and 1

The compared circuit is a system which reflects on a simple sign (voltage) with unequivocal voltage and gives a double signal based on the evaluation. vp is the beat- tension entered, updated to the incomparable comparator terminal, with the Vn reference- tension finished with the bad comparator terminal [4]. vp is the beat-tension entry terminal. Untendered Speed Comparators are more disturbing when the voltage of load decreases. To increase unreasonable speed, larger transistor systems are necessary to compensate for the decreased transmission voltage in different ways in an offered innovation. It moreover technique that more beyond words and vitality is required. but, low-voltage activity impacts in restricted regular mode enter run, that is essential in numerous over the top speed ADC designs, which incorporates Flash ADCs [5]. The presentation of inordinate speed simple to computerized converters (ADCs) fundamentally relies upon the comparator. The transformation from simple to virtual structures generally involves a comparator movement when the expense of simple voltage is contrasted and a few favored expenses at some point in time. The ADC is a voltage contribution. The entry sign in ADC is parallel to the computerized sign. Comparator examines two flows or voltages and creates a computerized yield on the basis of the evaluation.

The major component of a CMOS comparator contrasts an information sign and the reference signal and creates the yield in like manner. A comparator comprises of an exorbitant advantage differential enhancer. Comparator is one of the developing squares in limit of the simple to-virtual converters without which the system of information change can't take area. In vogue comparators are quick. Some high-pace ADCs, alongside glimmer ADCs, require high-speed, low-quality comparator.

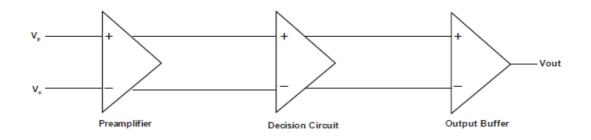

In a comparator there are three main aspects; the main grade is the pre-enhancer organization. The input signal to the comparator is enhanced to this degree. The second degree is a positive level of remarks. that is for the most part used to end up mindful of the info sign that is unreasonable or low. The absolute last degree is the decision-making degree and a yield cushion degree. directly here the essential reason of cradle is to expand the insights that is gotten and bring a virtual sign as its yield. Planning a comparator is practiced by utilizing considering enter regular mode assortment, control dispersal, proliferation deferral and area of the entire chip.

#### A. WORKING OF COMPARATOR

In most easy to-advanced converters (ADCs) the comparator is one of the main obstruction constructions. Many ADCs with ribbon ADC involve poor performance and high speed comparisons with the small processor region. Fast comparators in CMOS innovations in ultra-depth submikrometrics have the negative impacts of small load voltages, particularly in view of the fact that device border voltages have not been scaled at an equal pace because of the present CMOS methodology's production voltages.

#### Figure 3.2: Comparator Block diagram

In most easy to-advanced converters (ADCs) the comparator is one of the main obstruction constructions. Many ADCs with ribbon ADC involve poor performance and high speed comparisons with the small processor region. Fast comparators in CMOS innovations in ultra-depth submikrometrics have the negative impacts of small load voltages, particularly in view of the fact that

device border voltages have not been scaled at an equal pace because of the present CMOS methodology's production voltages. The second (regenerative stage) stage consists of two inverters connected by cross, each information being linked to the other's output. The regenerative stage and its subsequent steps in CMOS- based hook consume low static power because NMOS or PMOS transistors exchange power on the ground[4]. Control dissemination and transistor control are becoming increasingly important in many applications. Should the comparator speed be necessary, its regenerative activity could start on the half way between the supply of power and the ground. In any case the use of static power, for example, decreases in the ordinary comparator, thereby further increasing transistors by decreasing the speed.

#### **B. CONVENTIONAL DYNAMIC COMPARATOR**

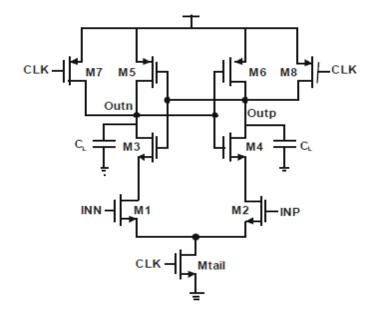

Figure 3.3: Schematic diagram of the conventional dynamic comparator.

Different designs were taken into account in a full evaluation of the delays in vibrant comparators .Furthermore, a new, distinctive comparator out of the cabinet, which does not involve the assisted voltage or stacking of an excessive number of transistors, is given, essentially based on the dual-tail framework suggested in [10].Basically, a lock delayed time is essentially reduced by including a few smaller transistors to the usual dynamic dual-tail comparator. The variety also results, when contrasted to a standard dynamic comparator and two-tail comparator, in financial reserve funds monster control.

The need for extremely low quality, territorial-service and high-speed simple, state- of - the-art converters is closer to using dynamic regenerative comparators in order to enhance speed and efficiency. An evaluation could be made of the delays in the vibrant comparators and structural joints determined. Fashioners can create an instinct from systemic articulations around the main persons to replace the comparator and can fully examine the replace outs in a strong compared manner. The favorable observations throughout the regeneration are strengthened, which leads to an unimaginably decreased deferred moment, without entangling the structure or the guidance including some transistors. High information impedance is the normal leeway of married hair, no frictional entry of electricity, railways to train and the correct force for complaint and confusion. High information

ISSN: 1007-6735

impedance in view of how parashic transistor capabilities are never legitimately reversed again in the rate of exchange of output hubs, the formatting of enormous transistors in order to limit equilibrium is conceivable for miles.

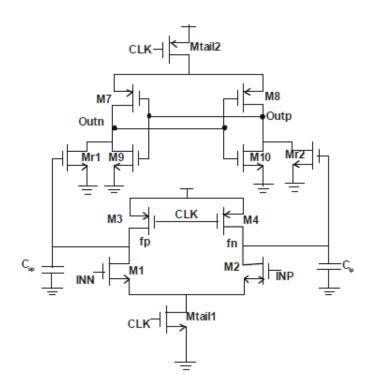

#### C. CONSERVATIVE DOUBLE- TAIL DYNAMIC COMPARATOR

Figure 3.4 shows the scheme of the traditional double tail comparator. This system is stacked less than standard dynasty comparator, and therefore can function at reduced load voltages.

Figure 3.4: Dynamic double-tail standard comparator scheme

This comparator operation is provided below. Download the transistors M3 - M4 precharge fn and fp to VDD during the resetting phase (CLK=0, Mtai1landMtail 2 swipe off), resulting in transistors MR1 and MR2 unloading the nodes to the earth. During the decisional phase (CLK = VDD, Mtai1landMtail 2 is enabled), M3 - M4 is disabled and the voltages at the fn / fp node start decrease with the rate defined by IMtail / Cfn(p) and, above this, a differential voltage dependent upon the input – Vf n(p) is created. The MR1 and MR2 intermediary phase is translated into the cross-connected inverter by ~Vf n(p) with excellent entry and output protection[6].Comparator with double tail Clocked renewable comparators discovered several apps in many high-speed ADCs, because their powerful positive feedback in regenerative lock enables them to perform quick activities in a spectrum of apps. The various comparators are based on the double thigh structure, which can be built using different technologies, for their maximum performance in various applications in low voltage application. Dual entry, dual output inverter phase, suited to high-speed analog-to-digital converters, have been designed for different apps.

## 4. RESULT & DISCUSSION

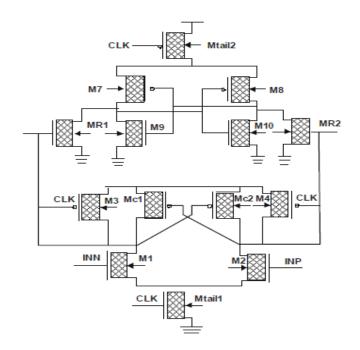

## Figure 4.1: Dynamic double-tail comparator using GNRFET

The above figure shows the dynamic double-tail comparator using GNRFET. It is used in low voltage application.

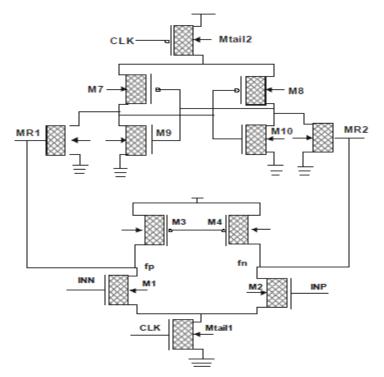

Figure 4.2: proposed Dynamic comparator

The figure above shows the Dynamic Comparator proposed.. Here we are using the GNRFET because it is having low delay, low average power and energy.

|                  |                         | GNRFET     | based | Proposed |

|------------------|-------------------------|------------|-------|----------|

| circuit1         | MOSFET based Comparator | Comparator |       |          |

| Average Power(W) | 5.56E-07                | 7.43E-09   |       |          |

| Delay(S)         | 4.09E-10                | 4.02E-11   |       |          |

| Energy(J)        | 2.28E-16                | 2.99E-19   |       |          |

#### Table 4.1: comparison table 1

Table 4.1 shows the comparison between the MOSFET Comparator and Proposed Comparator based on mean power, delay and energy. The GNRFET-based Comparator Proposed Comparator low in MOSFET-based Comparator is shown here to have low average power and the delay in the GNRFET-based Proposed Comparator high in the MOSFET-based Comparator is low and the power in the MOSFET-based MOSFET- based Comparator low is high.

#### Table 4.2: comparison table 2

|                  | MOSFET based Pro | posed GNRFET | based Proposed |

|------------------|------------------|--------------|----------------|

| circuit2         | Comparator       | Comparator   |                |

| Average Power(W) | 5.93E-07         | 8.10E-09     |                |

| Delay(S)         | 3.23E-10         | 3.98E-11     |                |

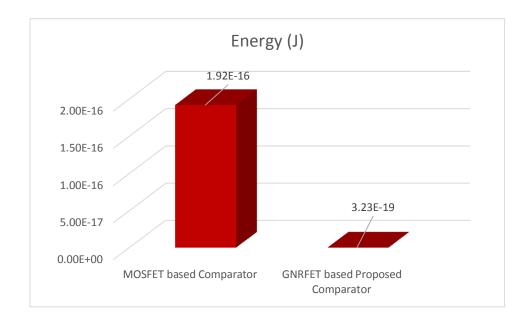

| Energy(J)        | 1.92E-16         | 3.23E-19     |                |

The table 2 is shows the comparison table of MOSFET based Proposed Comparator and GNRFET based Proposed Comparator. Here we can see the average power, delay and energy of MOSFET based Proposed Comparator and GNRFET based Proposed Comparator. The average power is high in GNRFET based Proposed Comparator and low in MOSFET based Proposed Comparator and the average power is high in GNRFET based Proposed Comparator and low in MOSFET based Proposed Comparator and the average power is high in GNRFET based Proposed Comparator and low in MOSFET based Proposed Comparator.

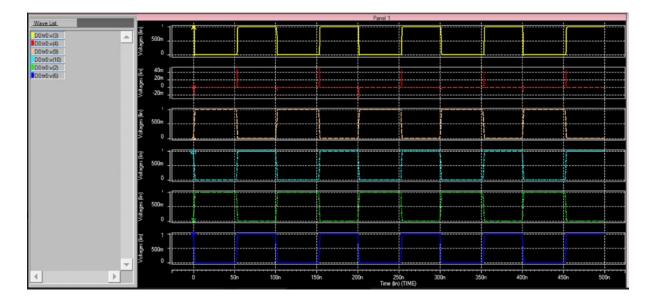

Fig 4.3: Input output waveform of proposed system

The figure 3 shows the input and output wave form of proposed system.

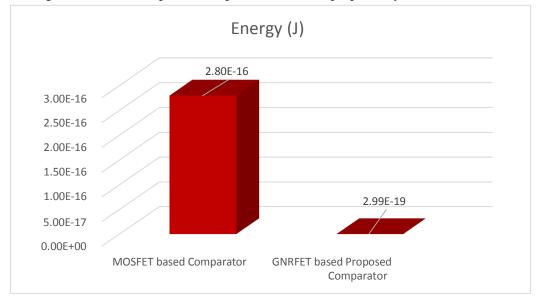

## Figure 4.4: Energy of MOSFET based Comparator and GNRFET based Proposed Comparator

In figure 4.4 shows the energy diagram of MOSFET based Comparator and GNRFET based Proposed Comparator. Here we can see the energy is less in GNRFET based Proposed Comparator and high in MOSFET based Comparator.

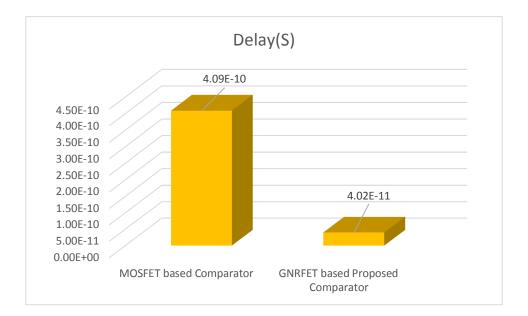

## Figure 4.5: Delay of MOSFET based Comparator and GNRFET based Proposed Comparator

In figure 4.5 shows the Delay diagram of MOSFET based Comparator and GNRFET based Proposed Comparator. Here we can see the delay is less in GNRFET based Proposed Comparator and high in MOSFET based Comparator.

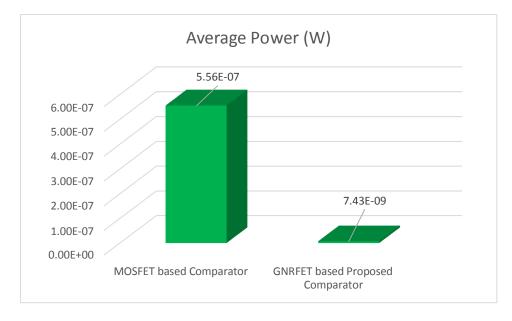

## Figure 4.6: Average power MOSFET based Comparator and GNRFET based Proposed Comparator

In figure 4.6 shows the average power diagram of MOSFET based Comparator and GNRFET based Proposed Comparator. Here we can see the average is less in GNRFET based Proposed Comparator and high in MOSFET based Comparator.

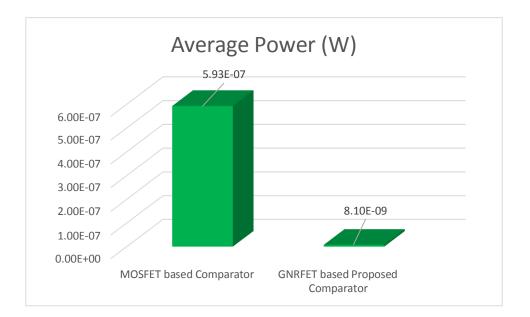

# Figure 4.7: Average power of MOSFET based Proposed Comparator and GNRFET based Proposed Comparator

The graph figure 4.7 diagram shows the Average power of MOSFET based Proposed Comparator and GNRFET based Proposed Comparator. here we can see the average power is less in GNRFET based Proposed Comparator and high in MOSFET based Proposed Comparator.

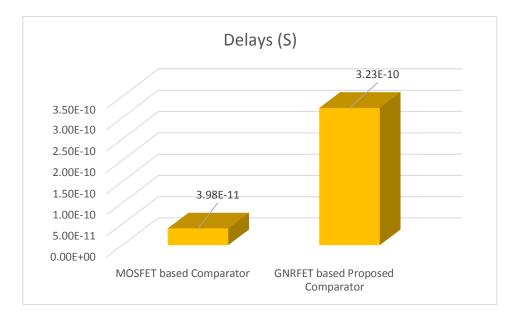

## Figure 4.8: Delay of MOSFET based Proposed Comparator and GNRFET based Proposed Comparator

The above figure 4.8 graph diagram shows the Delay of MOSFET based Proposed Comparator and GNRFET based Proposed Comparator. here we can see the delay is less in GNRFET based Proposed Comparator and high in MOSFET based Proposed Comparator.

#### Figure 4.9: Energy of MOSFET based Proposed Comparator and GNRFET based Proposed Comparator

The above figure 4.9 graph diagram shows the energy of MOSFET based Proposed Comparator and GNRFET based Proposed Comparator. here we can see the energy is less in GNRFET based Proposed Comparator and high in MOSFET based Proposed Comparator.

**Conclusion:** - hence, here we are comparing different circuits like MOSFET based Comparator and GNRFET based Proposed Comparator and MOSFET based Proposed Comparator and GNRFET based Proposed Comparator and finding the different parameters in different comparator. We get energy, average power and delay in the parameters here. In the proposed GNRFET-based comparator, the energy, average power and delay are less important. The efficiency boundaries of a field-effect transistor (FET) with multilayer GNRFET and CO2 Nano tube (CNT) FET are measured and comparable with those of a single-layer GNRFET.

## **5. CONCLUSION**

## A. GNRFET APPLICATIONS

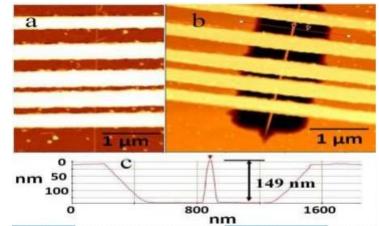

#### a. ROOM-TEMPERATURE HIGH ON/OFF RATIO IN SUSPENDED GNRFET

This shows ambpolar impact qualities, and high in and out ratios at room temperature can be recorded with a technique known as controlled current strengthening in moderately large graphene nanoribbons (15 nm ~50 nm). Current reinforcement regulated here is used to reduce the trapped GNR to chamber heat in order to enter a containment pocket.

Figure 5.1: AFM pictures of FET gadgets comprise of a GNR reached by Au cathodes previously (an) and after (b) suspending the GNR. (c) Line profile of the top segment of the suspended GNR.

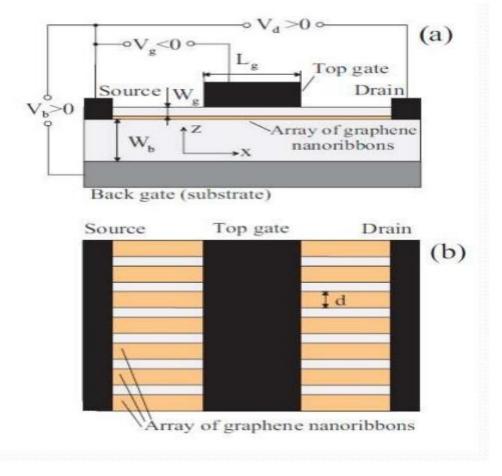

#### b. CURRENT-VOLTAGE CHARACTERISTICS OF A GNRFET

G-FETs also involve developing the flat junction between n-p-n (or p-n-p) and the controlled (bottom) door and the vitality obstacle. For GNR-FET improvement apps, this model can be used.

Figure 5.2 Graphene nano-ribbon structure

Another application is: the wafer-scale, epitaxial layer

- > Graphene nanoribbon field-impact transistors, for broad applications.

- Graphene Nano-ribbon field-impact transistors can be used as low-check frames in various gadgets

- > Device GNRFET performances in the presence of line-edge roughness nanoribbons

#### c. OTHER USES

At the point when current go through an ON transistor, there are for the most part electrons with a great deal of vitality. On the off chance that an electron have adequate vitality, it can bounce from the channel into the gate oxide. This hot-transporter infusion sways a negative charge in the gate oxide. In this way thusly these hot electrons develop in the gate and can prompt for all time change the attributes and conduct of a transistor.

Another influence is recognized with the door voltage, called inclination temperature precariousness. Electrons are taken in to the voltage while the voltage is attached to the door. Electrons could be maneuvered into the door oxide given appropriate moment. Dislike the infusion of hot-administration, most electrons never infiltrate deep into the gate oxide again, and the effect can usually be turned over if there is no voltage. The voltage fitted to the door can also shut down the gate oxide. Minute forms within the voltage or the material itself lead to small "traps" inside the oxide that can direct power. If that is sufficient

Eventually, the steel contacts which interface a transistor with its info sources can also develop as detached In contemporary times, small fluxes can free steel molecules and form hole associations. Given time, the hole will be enlarged until the metal and the transistor are associated. These effects are referred to as electromigration.

Both the MOSFET and GNRFETs offer each of the four impacts. This causes a lapse in circuits using NMOS and pMOS over the years. Be that as it may, since pMOSFETs mark over the bottom door voltages, they are strictly unable to prevent inclination temperatures insecurity. This is a GNRFET's prize: they are not tortured by this unevenness due to the fact they have neither p-type nor n-kind publications. To conclude, four outcomes undertake to create transistors more experienced and all four are accessible in each MOSFETs and GNRFETs.

Exchange expenses with transistors of graphene. As the electrical properties of the substratum can never again be used by graphene transitoMoreover, it shouldn't be doped with graphene.rs, the low top of the silicone line could be used. This entails the third-highest assembly cost – doping gases. In addition, the expenses of veil and photo resistors can be even lower, as the easier generation technology does not include doping. These cost reductions are counterbalanced by the costs of assembly and storage of graphs for miles reasonable. GNRFETs may definitely be inexpensive to produce in any situation than MOSFETs.

#### REFERENCES

- [1] Yijian Ouyang et.al, "Scaling Behaviors of Graphene Nanoribbon FETs: A Three Dimensional Quantum Simulation Study" IEEE Trans. Volume: 54, Issue: 9 ,Sept. 2007

- [2] Abhijith A Bharadwaj et.al "Design and Performance Comparison of finFET, CNFET and

GNRFET based 6T SRAM" International Journal of Science and Research (IJSR), 2013

- [3] PRAVEENA KUMARI et.al, "Design and Analysis of 16bit Ripple Carry Adder and Carry Skip Adder Using Graphene Nano Ribbon Field Effect Transistor (GNRFET)" International Journal of Innovative Science and Research Technology, Volume 2, Issue 7, July– 2017

- [4] Preetika Sharma et.al, "Effect of temperature on the conductance of GNRFET" Conference paper, April 2016

- [5] Huei Chaeng Chin et.al, "Enhanced Device and Circuit-Level Performance Benchmarking of Graphene Nanoribbon Field-Effect Transistor against a Nano-MOSFET with Interconnects" Hindawi Publishing Corporation Journal of Nanomaterials Volume 2014

- [6] Amit Sangalet.al, GNRFET as future low power devices, conference paper September 2013

- [7] IrajSadeghAmiri, MahdiarGhadiry "Analytical Modelling of Breakdown Effect in Graphene Nanoribbon Field Effect Transistor," Springer publisher, 2017.

- [8] M. Gholipour and N. Masoumi, "Graphene Nanoribbon Crossbar Architecture For Low Power And Dens.

- [9] Y.-Y. Chen, A. Rogachev, A. Sangai, G. Iannaccone, G. Fiori and D. Chen, "A SPICE-Compatible Model of Graphene Nano-Ribbon Field-Effect Transistors Enabling CircuitLevel Delay and Power Analysis Under Process Variation," in EDAA, 2013

- [10] S. Kim, S. Kosonocky, D. Knebel, K. Stawiasz, and M. Papaefthymiou, "A Multi- Mode Power Gating Structure for Low-Voltage DeepSubmicron CMOS ICs," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 54, no. 7, pp. 586–590, 2007.