# **Review of Different Topologies of Multi-Level Inverter**

Yogesh Joshi

Department of electrical engineering NITTTR Chandigarh yogeshjoshi8090@gmail.com

### Dr. Shimi S.L

Assistant professor, Department of electrical engineering NITTTR Chandigarh Shimi.reji@gmail.com

Abstract: A Multi-Level inverter (MLI) is operated for maximum power, high voltage applications that change DC power into AC power. Traditional power electronic converters are equipped for creating a result voltage (volt) that changes between two-volt levels. The MLI creates the ideal result voltage from numerous levels or degrees of DC voltage at its input. These MLIs are grid incorporated for renewable energy extraction, for example, sun-based photovoltaic (PV) frameworks. The Multi-Level Inverter (MLI) gives a smoother stepped output waveform. Waveform perfection is connected with voltage levels as the voltage level builds, the waveform becomes smoother, yet intricacy increments. The PWM generates an output voltage that is in steps with low harmonic (LH) content and can infuse a sinusoidal gate current with a good power factor (PF). Pulse Width Modulation based framework associated with photovoltaic can work at a lower switching frequency with decreased filtering requirements. Sun-based PV boards of inconsistent power ratings are appropriately associated with DC connect voltages of a reasonable proportion for an asymmetrical cascade multilevel inverter. There are a few benefits of PWM, for example, higher DC connect voltage, low electromagnetic point of interaction (EM), and less harmonic distortion, however, to accomplish these inverters require more switches, complex Pulse Width Modulation (PWM) control, need intricacy plan, control circuits and isolated power supplies. The various topologies of MLI are Multilevel Modular Converter (MMC), Cascaded H-Bridge Converter (CHBC), Flying Capacitor Multilevel Inverter (FCMLI), and Blocked Diode Inverter (BDI). The different application regions incorporate its utilization as an inverter with variable frequency drives, high voltage DC (HVDC) transmission, in pumps and in transports, and so forth. Point-by-point examinations and dissects of various control strategies utilized in single-stage and three-stage network-associated PWMs are likewise integrated into this paper for a superior comprehension and viability of past, present, and future improvements in photovoltaic frameworks.

Keywords: Multi-Level Inverter, PWM, Photovoltaic, THD, Switching Functions

## I. INTRODUCTION

The shortage of non-renewable energy sources and with no contamination impact, (Non-conventional Energy Sources) NCES is more prevalent in electric power generation [1]. The quick advancement of electronic power control methods in generation of the electrical power and the extra benefits are calculated by the sun oriented photovoltaic (PV) frameworks that are utilized in numerous modern and private applications like at home and in companies, etc.

Two Level Inverter is the inverter that produces output voltage or current with two distinct degrees of positive voltage and negative voltage. These types of inverters are counted as regular two-level inverter which works at a high switching frequency and switching losses and influence limitations for high voltage. It likewise faces Total Harmonic Distortion (THD), Electro Magnetic Induction  $\frac{dV}{dt}$ , and high voltage [2]. The level of THD is very high in the inverters which is counted as main problem. By interconnecting the power electronics devices with the high or medium level voltage grid these issues is very challenging. This is the main cause that we are switching onto the Multi-Level Inverter (MLI) topologies. The MLI idea was firstly presented in mid of the 1975 with MLI which was basically 3-level converters. If an inverter has various level in inverter so it is feasible to expand the power rating but due to this issue the device voltage rating in the inverter is diminishes. By using the various level of DC input voltage (V<sub>i</sub>), the MLI creates a smooth sine waveform.

Likewise, to limit THD in the inverter current, the necessary thing is the switching frequency of Pulse Width Modulation (PWM) is normally extremely high, so the switching losses become very high. There are a few existing traditional PWM topologies framework are associated with PV frameworks, for example, diode-clamped inverter (DCI) [3], capacitor-clamped inverter (CCI) [4], Cascade H-bridge (CHB) Multi-Level Inverter [5-6] and hybrid MLI [7-8]. All the mentioned inverters are worked on the higher frequency and in any case, the power losses of these inverters are typically high, since more power switches are utilized for MLI.

### Journal of University of Shanghai for Science and Technology

The sun based photovoltaic system produce around 1% of the complete power consumed around the world. Between independent and matrix associated photovoltaic frameworks, the last option address over the vast majority of every photovoltaic establishment. This is because of the lower establishment cost, versatility for future development, decreased support, and higher unwavering quality of grid connected frameworks contrasted with independent frameworks.

A multilevel approach guarantees a decrease in harmonic because of sinusoidal result voltages: in this way grid filters become immaterial, bringing about diminished framework cost and intricacy.

The idea of a modular converter geography has the inborn capacity to further develop unwavering quality, since a shortcoming module can be circumvented, permitting the activity of the whole circuit without fundamentally influencing execution.

Numerous MLI topologies have been concentrated in last years, introducing benefits and impediments during the activity or assembling of the converters. To take care of the issues of regular MLIs. Subsequently, the intriguing elements can be summed up as follows

- 1. Decreased THD without filters

- 2. Lessen the necessary size of the filters

- 3. Flight of stairs waveform that is more like a sine wave

- 4. Works at key and high switching frequency

- 5. Less switching losses

- 6. Good power quality

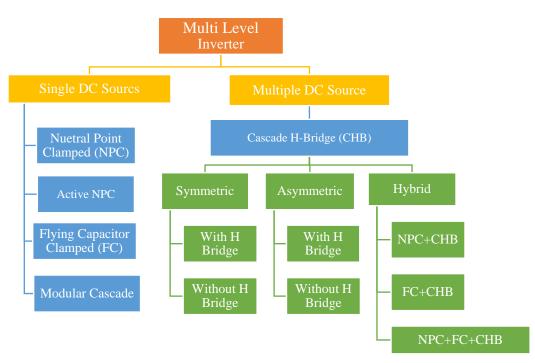

Fig. 1. Types of Multi-Level Inverter [2]

As the number of power semiconductor switches is required in a MLIs which is a specific downside. To adds intricacy to the framework each switch has a related gate driver circuit. Due to these extra switches which increases the costing the general framework is costlier as compared to the conventional inverters. As of late, accentuation has been put on lessening circuit intricacy by decreasing the numbers of the gate driving circuits associated with the power electronics switches. So, this article presents the various topologies of Multi-Level Inverters with the related designs and the benefits and inconveniences of each circuit.

## II. LITERATURE REVIEW

An device which converts direct current into alternate current at a characterized frequency and result voltage is known as an inverter which is comprises with power electronic devices. This regular inverter has significant switching losses, as well as cut-off points, and works at a high switching

### Journal of University of Shanghai for Science and Technology

frequency for high power and high voltage applications. Switching losses and unsettling influences because of harmonics, electromagnetic interference, and high voltage loads are difficulties one should survive. The presence of a lot of worldwide harmonic distortion is likewise an issue. The immediate association of electronic power changes to the high and medium voltage network is troublesome because of these issues. This requires the utilization of a multilevel inverter with a different topology [9]. Albeit most MLI research currently centres around low voltage applications, essentially utilized in environmentally friendly power frameworks require high voltage frameworks above kV. In sun powered (solar) applications, MLI geographies have further developed effectiveness while diminishing EMI and centre or core losses. Free DC sources are made from PV exhibits and can be effectively modularized contrasted with other MLI, for example, cascade H-bridge PWM engineering [10]. Thusly, formal methodology has their position in the formation of control by plan frameworks. The principle capability of a power MLIs is to generate the ideal voltage from different DC voltage levels. In this way, multi-level power inverters are great for giving the high power expected by enormous electric engine frameworks.

In multi-level inverters (MLIs), power transformation parts and variable voltage sources are utilized. The capacity of MLI is to make output voltage  $(V_0)$  wave form with a more extensive symphonies reach and accomplish higher voltages with a restricted most extreme rating, MLIs are reasonable for high voltage applications. Because of the simplicity of execution of the power converters the exchanged control has drawn in a ton of consideration. The sustainable power sources or power converters are utilized to associate unpredictable energy sources to electrical organizations and to work on the proficiency of sunlight-based chargers and wind turbines. Be that as it may, in certain models, the quantity of switches increments emphatically, prompting an expansion in the quantity of factors and entangling regulator plan. Thus, formal procedures are simply used partially in building control components that are right by the plan. The primary capability of a multi-level power converter is to blend the ideal voltage from different DC voltage levels [9]. Nonetheless, to make bipolar levels, utilizing every one of the switches isn't required. The resulting voltage is parted into equal parts in this staggered hybrid plan. One section is known as the level creation part and is liable for making levels of positive extremity. This section requires high-frequency changes to make the expected levels. The switches on this part should have the option to rapidly change. The extremity age segment, which is a low-frequency segment working at line frequency [11], is liable for producing the extremity of the resulting voltage. A rising assortment of modern applications have required higher power hardware as of late. Traditionally the power semiconductor switches are interconnected to a medium voltage network [12]. Despite the fact that AC variable frequency drives are notable, high-power and medium-voltage inverters have as of late turned into the focal point of study. Customary two-level inverters in high-power applications, apparently, present a few challenges, because of their capacity to work at high switching frequencies while delivering lower order harmonic, MLIs have produced extensive interest in high-power applications.

An innovative design of a MLI with a lower number of switch counts is proposed by chillappagari et.al and the unwavering quality of the MLI setup is improved by examining the adaptation to noncritical failure activity [13]. According to the performance examination, it was seen that the innovative design inverter is having sufficient capacity to endure open circuit (OC) faults not just for the single switch and furthermore for various switches. Even this keeps with the consistent voltage pre-faults and post-faults activity with the assistance of a transformer. And furthermore, to improve the efficiency of the inverter, it was seen that the assistance of a multi-transporter PWM switching control system with the multi-Level inverter. According to Verma et.al [14] if one increases the number of switches the harmonics and EMI are reduced as well as the performance of the inverter is increased according to the desire value. But due to this the switching losses and cost are also increased.

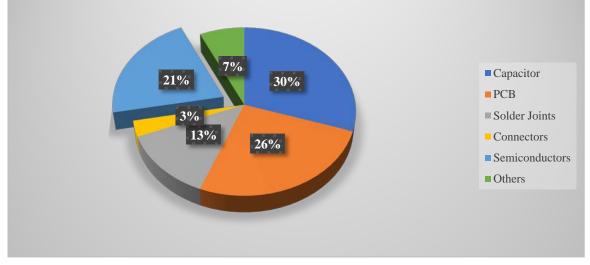

Fig. 2. Failure Rates of Different Components of MLIs

Das et. al [15] examinations the presentation of the decreased number of switches in asymmetrical MLI for a network associated PV framework regarding losses and productivity. It is very well known as the productivity of the regular MLI is 97.90%. The presentation of the voltage as well as the ongoing regulator for the inconsistent PV sources is  $1000 \text{ W/m}^2$ . The reproduction aftereffects of the DC interface capacitor voltages, inverter voltage and network current under consistent state conditions as well as factor illumination are dissected and introduced. The DC connect voltage adjusting of PV boards of inconsistent power rating is tried with uniform irradiance. The reproduction consequences of the above matrix tied framework under factor network voltage are additionally broke down.

## III. CONCEPT OF MULTILEVEL INVERTERS

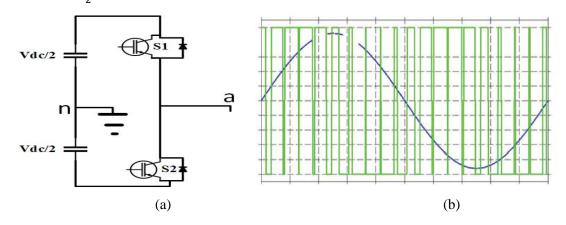

Figure 3 part (a) demonstrate the regular two-level inverters which ordinarily produce a result of AC voltage from an input of DC voltage. The AC output voltage showcased in fig. 3(b) is produced by using PWM switching plan.

To make a soother output waveform which is demonstrated in the fig. 3(c), the few DC voltage levels are introduced in the MLIs topologies. The resulted waveform has less total harmonic distortion (THD) and lower dv/dt losses. As far as the expansion in voltage levels is increased the circuit configuration is more complicated. To overcome with this issue, one can have a convoluted switching regulator circuit.

The basic circuit diagram of a regular three-level inverter is demonstrated in fig. 3 (d). Each stage of the three-level inverter produces the three level of voltage given by  $\frac{V_{dc}}{2}$ , 0,  $-\frac{V_{dc}}{2}$ . The basic construction of the three-level inverter is like as a regular two-level inverter, the main difference is the clamping diodes in the middle of between the two valves and are associated with the unbiased between two capacitors. The capacitors go about as DC bus voltage sources, everyone is accused of the voltage  $\frac{V_{dc}}{2}$ .

Fig. 3 (a) Two-Level Inverter without PWM Technique (b) Output Voltage of PWM Inverter (c) 3-Level, 5-Level & 7-Level Output Waveform (d) 3-Level Inverter [1]

One can want to increase the number of levels so we have to use another phase leg. At the midpoint, we can change the voltage level to Zero. Clamping diodes are responsible to hold the voltage to zero with the neutral point. To increase the output of the inverter the clamping diodes and capacitors are introduced.

The first practical Multi-Level Inverter (MLIs) are unbiased point or neutral point PWM topology with a clamping diode of MLIs. It was first projected by Takashi et.al in 1981 [16]. It is otherwise called an unbiased point converter. In a multi-level inverter if one can choose a level-m diode inverter requires a number of switching devices which is calculated by 2m-2, the number of input voltage sources calculated by m-1, where the number of diodes required to form it, are: (m-1) (m-2). V<sub>dc</sub> is the voltage present at the terminals of every diode and of the switch. A five-level diode inverter is exhibited in fig. 4.

This topology faces specialized challenges for high-power converters. It requires high-velocity clipping diodes which will be under switch reverse recovery stress. Plan intricacy is the main issue because of the series association of diodes.

Fig. 4. Five-Level Diode Clamped MLI [17]

| S. No. | Particulars      | <b>Regular Inverter</b> | MLI |

|--------|------------------|-------------------------|-----|

| 1      | THD              | High                    | Low |

| 2      | Switching Stress | High                    | Low |

Table 1. Comparison 2-Level 3-Level Inverter

### Journal of University of Shanghai for Science and Technology

| 3 | Used for High Voltage Application | No   | Yes |

|---|-----------------------------------|------|-----|

| 4 | High Voltage Level                | No   | Yes |

| 5 | dv/dt                             | High | Low |

| 6 | EMI                               | High | Low |

| 7 | Switching Frequency               | High | Low |

| 8 | Switching Losses                  | High | Low |

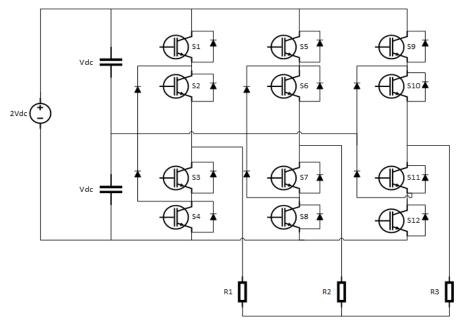

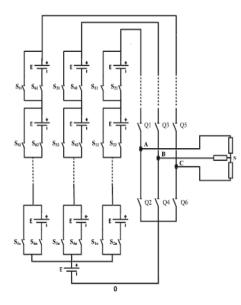

The cascaded  $3-\phi$  H-bridge inverter (HBI) utilizes separate DC sources or capacitors as displayed in fig. 5. It required a smaller number of parts to drive in each voltage level. The power conversion cell is associated in the series. The H-bridge comprises combination of the capacitors and switches pair. As in the output voltage which produces a sinusoidal result. The series connected H-Bridge cell is produce the three unique degrees of DC voltages like zero, positive and negative voltage. Assuming that there are m cells in the inverter and the quantities of result voltage levels will be (2m+1). A 5-level HBI is showed in fig. 6. Similarly, the Table 1 shows the basic difference between the two-level and three-level inverter. Similarly, the 9-level inverter is also shown in the fig. 7 with the switching pattern and the THD of 9 level MLI is about 8.53% [38].

Fig. 5. Power Circuit of 3-Phase MLI [17]

Fig. 6. General Cascade H-Bridge MLI [18]

| $S_1 S_2 S_3 S_4 S_5 S_6 S_7 H_1 H_2 H_3 H_4 D_1$ | $V_o$      | $C_1$ | $C_2$ |

|---------------------------------------------------|------------|-------|-------|

| 000100001011                                      | 0          |       | -     |

| 000100010101                                      | 0          |       | -     |

| 100100010011                                      | $+V_{dc}$  |       | -     |

| 100100001101                                      | $-V_{dc}$  |       | -     |

| 011001110010                                      | $+2V_{dc}$ | V     |       |

| 011001101100                                      | $-2V_{dc}$ |       |       |

| 000110110011                                      | $+3V_{dc}$ |       |       |

| 000110101101                                      | $-3V_{dc}$ |       |       |

| 001010110010                                      | $+4V_{dc}$ |       |       |

| 001010101100                                      | $-4V_{dc}$ |       |       |

**(b)**

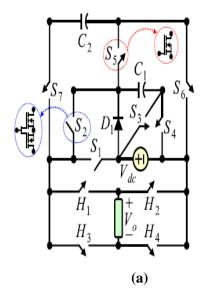

### Fig. 7. (a) 9-Level Inverter, (b) Switching Pattern

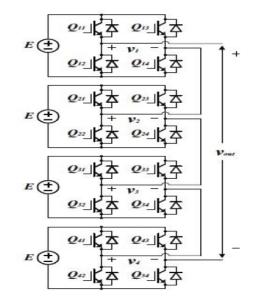

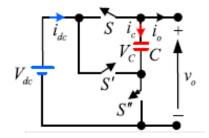

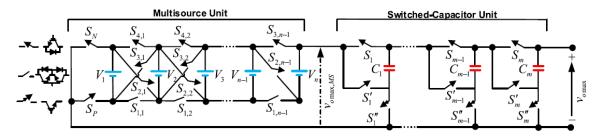

One multi-level inverter (MLI) is configured with slandered H-bridge inverter to generate negative voltage level inverter. The fig. 8 shows the basic multi-source (MS) switched capacitor (SC) MLI which includes three switches (two are capacitors and one is dc source). By the use of switches S, S' and S" the capacitor voltage is thus charged and set to the magnitude of dc source. Similarly, the fig. 9 demonstrate the a MLI with two units the first one is the MS unit and the other one is SC unit in several modes. The operation of these several SC units follows the basic operation of standard SC unit shows in fig. 8 [40]. The THD of voltage and current is 1.83% and 0.95% respectively. Table 2 demonstrate the comparison of different level MLI in various manner.

Fig. 8. Basic Multisource Switched Capacitor MLI [40]

Fig. 9. Extended Multisource Switched Capacitor Topology [40]

| S. No. /<br>Ref | Level of<br>Inverter | No. of<br>Switches | No. of<br>Capacitor | No. of<br>Diodes | No. of<br>Sources | THD   |

|-----------------|----------------------|--------------------|---------------------|------------------|-------------------|-------|

| 1 [40]          | 9                    | 9                  | -                   | -                | 2                 | 4.38% |

| 2 [41]          | 9                    | 9                  | 2                   | 2                | 1                 | 5.13% |

| 3 [42]          | 7                    | 7                  | 1                   | 2                | 2                 | 3.3%  |

| 4 [43]          | 7                    | 8                  | -                   | -                | 3                 | 20%   |

| 5 [44]          | 11                   | 20                 | -                   | -                | 5                 | 8.68% |

| 6 [45]          | 11                   | 10                 | -                   | -                | 4                 | 3.7%  |

Table 2. Comparison of Different level MLI

## **IV. COMPARISON OF DIFFERENT MULTI-LEVEL TOPOLOGIES**

The neutral Point Clamped (NPC), Flying Capacitor (FC) and Cascaded H-Bridge (CHB) inverters used clipping diodes instead of the power switching devices as discussed in the review but they have disadvantages. For FC Topology the DC Link capacitor zero voltage level is introduced. When we compare the first two topologies i.e., NPC and FC the number of components is reduced and if we compare the NPC with CHB the conduction losses are seen very less. Accordingly, different topologies are compared in the table 3 [19-35].

|        | Comparison of different MLIs          |                                     |                                   |  |  |

|--------|---------------------------------------|-------------------------------------|-----------------------------------|--|--|

| S. No. | Parameters                            | Different MLI<br>Topologies [19-35] | Switching Function<br>of MLI [29] |  |  |

| 1      | Switching Losses                      | Absent                              | Present                           |  |  |

| 2      | Complexity                            | Less                                | High                              |  |  |

| 3      | Installation Area and Cost            | Low                                 | High                              |  |  |

| 4      | Applicable of High-Power Applications | Yes                                 | No                                |  |  |

| 5      | THD                                   | Low                                 | High                              |  |  |

| 6      | Switching Devices                     | Less                                | High                              |  |  |

| 7      | Power Quality                         | High                                | Less                              |  |  |

| 8      | Less EMI                              | Yes                                 | No                                |  |  |

| 9      | Efficiency                            | High                                | Low                               |  |  |

Table 4 concluded the comparison between conventional and reduced switch MLIs. The design that includes Active Front End (AFE) is uses least number of switches in MLIs when it introduced with the single phase MLIs, similarly for 3-Phase AFE design provide a best implementation when compared to the single-phase MLIs. The switches count is less by 2 and 4 for the HH Cell and Semi-Reduced Cell respectively. When a controller came into the picture so it can be seen that the single-phase is more complex when compare to 3-Phase MLIs. And the reduced cell can provide the output level as (n+1) only, where n is the number of switches. Table 5 demonstrate the comparison of single-Phase power cell used for different number of switches like 8, 6 and 4 used in HH Cell, Semi-reduced cell and for reduced cell respectively. When we reduce the count of switch the current rating of the switches is increased proportionally. And this reduction in the switches for HH cell can be achieved by the half-bridge active front end inverter. Similarly, the reduction in the switch count can be achieved Cell [37]-[39].

| Configuration of Cell<br>(3-Phase Power Cell) | <b>Conventional Cell</b> | Reduced Switches                  |

|-----------------------------------------------|--------------------------|-----------------------------------|

| Switch Count                                  | 10 (10 Level MLI)        | 8 (As compared with 10 Level MLI) |

| Level of output voltage (V <sub>0</sub> )     | 2n + 1                   | 2n + 1                            |

| Switches Current                              | I <sub>in</sub>          | 2 <i>I</i> <sub>in</sub>          |

| Costing of Switches                           | 1 (Reference Cost)       | 0.8                               |

| Conduction Losses of the<br>Switches          | 1 (Reference Cost)       | 4                                 |

| Switches Losses                               | 1 (Reference Cost)       | 0.8                               |

|                                               | -                           | 8                           |                    |

|-----------------------------------------------|-----------------------------|-----------------------------|--------------------|

| Configuration of Cell<br>(1-Phase Power Cell) | HH Cell                     | Semi-Reduced                | Fully Reduced      |

| Switch Count                                  | 8                           | 6                           | 4                  |

| Level of output voltage<br>(V <sub>0</sub> )  | 2 <i>n</i> + 1              | 2 <i>n</i> + 1              | <i>n</i> + 1       |

| Switches Current                              | 1.73 <i>I</i> <sub>in</sub> | 3.46 <i>I</i> <sub>in</sub> | Similar to HH Cell |

| Costing of Switches                           | 0.8                         | 0.6                         | 0.4                |

| Conduction Losses of<br>the Switches          | 3 (Reference)               | 11.97                       | 3                  |

| Switches Losses                               | 0.8                         | 0.6                         | 0.4                |

Table 5. Comparison between different Single-Phase Power Cell [37] [39]

## V. CONCLUSION

This paper concentrates every one of the geographies connected with the Multi-Level Inverter (MLI) and to lessen the switching devices or output level can be enhanced. Likewise limit the requirement for enormous number of switching devices in a flowed MLI, it assisted with reducing down the expense of establishment and size of inverter. It likewise centres around the benefits of MLI having a smaller number of switching devices. It additionally said about the various utilizations of MLIs. MLI with diminished number of switching devices can incorporate more sinusoidal waveform and it can likewise work on the result voltage, Total Harmonic Distortion (THD).

#### **REFERENCES**

[1] Amrouche, S. Ould, Djamila Rekioua, Toufik Rekioua, and Seddik Bacha "Overview of energy storage in renewable energy systems" *International journal of hydrogen energy 41, no. 45 (2016): 20914-20927.*

[2] Suresh, L. Padma. "A brief review on multi-level inverter topologies" In 2016 international conference on circuit, power and computing technologies (ICCPCT), pp. 1-6. IEEE, 2016.

[3] Rodriguez, Jose, Steffen Bernet, Peter K. Steimer, and Ignacio E. Lizama. "A survey on neutral-pointclamped inverters." *IEEE transactions on Industrial Electronics 57, no. 7 (2009): 2219-2230.*

[4] Dargahi, Vahid, Arash Khoshkbar Sadigh, Mostafa Abarzadeh, Mohammad Reza Alizadeh Pahlavani, and Abbas Shoulaie. "Flying capacitors reduction in an improved double flying capacitor multicell converter controlled by a modified modulation method" *IEEE transactions on power electronics 27, no. 9 (2012): 3875-3887.*

[5] Ding, K., Ka Wai Eric Cheng, and Y. P. Zou. "Analysis of an asymmetric modulation method for cascaded multilevel inverters" *IET Power Electronics 5, no. 1 (2012): 74-85.*

[6] Lezana, Pablo, José Rodríguez, and Diego A. Oyarzún. "Cascaded multilevel inverter with regeneration capability and reduced number of switches" *IEEE Transactions on Industrial Electronics 55, no. 3 (2008):* 1059-1066.

[7] Raushan, Ravi, Bidyut Mahato, and Kartick Chandra Jana. "Comprehensive analysis of a novel three-phase multilevel inverter with minimum number of switches" *IET Power Electronics 9, no. 8 (2016): 1600-1607.*

[8] Dharmaian Retnam, Binu Ben Jose, Ammasai Gounden Nanjappa Gounder, and Vasanth Ammasai Gounden. "Hybrid power electronic controller for combined operation of constant power and maximum power point tracking for single-phase grid-tied photovoltaic systems" *IET Power Electronics 7, no. 12 (2014): 3007-3016.*

[9] Anjali Krishna, R. "Dr L Padma suresh "A brief review on multilevel inverter topologies" Conference on Circuit" *Power and Computing Technologies [ICCPCT]* (2016).

[10] Feld, Gilles, Laurent Fribourg, Denis Labrousse, Bertrand Revol, and Romain Soulat. "Correct-by-design control synthesis for multilevel converters using state space decomposition" *arXiv* preprint arXiv:1407.3890 (2014).

[11] Kowstubha, P., K. Krishnaveni, and C. Sathyasri. "Development of 13 level cascaded H bridge" Int. J. Electr. Eng. Technol. 8, no. 1 (2017): 80-92.

[12] Patel, Purnesh, Rejo Roy, Albert John Varghese, And Satyadharma Bharti "A Review on Multilevel Inverter Having Switched Capacitor with Reduced Number of Insulated Dc Supplies" (2022).

[13] Chillappagari, Pavan Kumar, Karthick Nagaraj, and Madhukar Rao Airineni. "Open-circuit fault resilient ability multi level inverter with reduced switch count for off grid applications" *International Journal of Electrical and Computer Engineering 12, no. 3 (2022): 2353.*

[14] Verma, Kapil, and Akhil Gupta. "A review on switching function of multi-level inverter and applications." *In 2016 7th India International Conference on Power Electronics (IICPE), pp. 1-5. IEEE, 2016.*

[15] Das, Madan Kumar, Kartick Chandra Jana, and Akanksha Sinha. "Performance evaluation of an asymmetrical reduced switched multi-level inverter for a grid-connected PV system" *IET Renewable Power Generation 12, no. 2 (2018): 252-263.*

[16] Nabae, Akira, Isao Takahashi, and Hirofumi Akagi. "A new neutral-point-clamped PWM inverter" *IEEE Transactions on industry applications 5 (1981): 518-523.*

[17] Kumar, L. Sanjeev. "New Three-Phase Symmetrical Multilevel Voltage Source Inverter for VSC HVDC" 2022.

[18] El-Hosainy, A., Hamed, H. A., Azazi, H. Z., & El-Kholy, E. E. (2017). A review of multilevel inverter topologies, control techniques, and applications 2017 Nineteenth International Middle East Power Systems Conference (MEPCON). doi:10.1109/mepcon.2017.8301344.

[19] Babaei, Ebrahim, and Seyed Hossein Hosseini. "New multilevel converter topology with minimum number of gate driver circuits" *In 2008 International Symposium on Power Electronics, Electrical Drives, Automation and Motion, pp. 792-797. IEEE, 2008.*

[20] Khomfoi, Surin, and Leon M. Tolbert. "Multilevel power converters" In Power electronics handbook, pp. 455-486. Butterworth-Heinemann, 2011.

[21] Mariethoz, Sebastien. "Systematic design of high-performance hybrid cascaded multilevel inverters with active voltage balance and minimum switching losses" *IEEE Transactions on Power Electronics 28, no. 7 (2012): 3100-3113.*

[22] Sujitha, N., B. Karthika, R. Hemantha Kumar, and M. Sasikumar. "Analysis of hybrid PWM control schemes for cascaded multilevel inverter fed industrial drives" *In 2014 International Conference on Circuits, Power and Computing Technologies [ICCPCT-2014], pp. 745-750. IEEE, 2014.*

[23] Barzegarkhoo, Reza, Hossein Madadi Kojabadi, Bagher Karami, and Liuchen Chang. "A novel charge balancing control approach for a single phase 9-level inverter based on fundamental modulation strategy" *In 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), pp. 3791-3796. IEEE, 2016.*

[24] Soltani, Hamid, Jafar Adabi, and Firuz Zare. "Effects of switching time on output voltages of a multilevel inverter used in high frequency applications" *Australian Journal of electrical and electronics engineering 5, no.* 2 (2009): 149-159.

[25] Gupta, K. K., and Sonal Jain. "Topology for multilevel inverters to attain maximum number of levels from given DC sources" *IET Power Electronics 5, no. 4 (2012): 435-446.*

[26] Banaei, M. R., A. R. Dehghanzadeh, Ebrahim Salary, Hossein Khounjahan, and Rana Alizadeh. "Z-source-based multilevel inverter with reduction of switches" *IET power electronics 5, no. 3 (2012): 385-392.*

[27] Kaliamoorthy, Mylsamy, Vairamani Rajasekaran, Irudayaraj Gerald Christopher Raj, and Lawrence Hubert Tony Raj. "Generalised hybrid switching topology for a single-phase modular multilevel inverter" *IET Power Electronics 7, no. 10 (2014): 2472-2485.*

[28] Mohamad, A. Syukri, Norman Mariun, Nasri Sulaiman, and M. Amran M. Radzi. "A new cascaded multilevel inverter topology with minimum number of conducting switches" *In 2014 IEEE Innovative Smart Grid Technologies-Asia (ISGT Asia), pp. 164-169. IEEE, 2014.*

[29] Verma, Kapil, and Akhil Gupta. "A review on switching function of multi-level inverter and applications" *In 2016 7th India International Conference on Power Electronics (IICPE), pp. 1-5. IEEE, 2016.*

[30] Gautam, Shivam Prakash, Lalit Kumar, Shubhrata Gupta, and Nitesh Agrawal. "A single-phase five-level inverter topology with switch fault-tolerance capabilities" *IEEE Transactions on Industrial Electronics* 64, no. 3 (2016): 2004-2014.

[31] Gong, Renxi, Bo Xue, Jianfeng Liu, and Xinyu Zhang. "Power balance modulation strategy for hybrid cascaded H-bridge multi-level inverter" *Electrical Engineering 104, no. 2 (2022): 753-762.*

[32] Vivert, Miguel, Rafael Diez, Marc Cousineau, Diego Bernal Cobaleda, Diego Patino, and Philippe Ladoux. "Real-Time Adaptive Selective Harmonic Elimination for Cascaded Full-Bridge Multilevel Inverter" *Energies 15, no. 9 (2022): 2995.*

[33] Yu, Jingrong, Ruoxue Yu, He Wen, Xianfu Lin, and Kai Hu. "Simplified SVPWM-based SoC balancing strategy for three-phase cascaded H-bridge multilevel converter in off-grid energy storage systems" *International Journal of Electrical Power & Energy Systems 137 (2022): 107474.*

[34] Patel, Karishma, And Gaurang Patel. "A Review on Three Phase Grid Connected PV System Using Three Level Cascaded H Bridge Multilevel Inverter" 2022

[35] Zawawi, M. N. M., Z. M. Isa, M. H. Arshad, B. Ismail, and M. H. N. Talib. "Comparative Study of Multiphase 5-Level Cascaded H-Bridge Multilevel Inverter System" *In Journal of Physics: Conference Series, vol. 2312, no. 1, p. 012062. IOP Publishing, 2022.*

[36] Nallathambi, K. A. L. A. I. A. R. A. S. I. "An Extensive Review on Fault Detection and Fault-tolerant Control of Multilevel Inverter with Applications" *International Journal of Renewable Energy Research* (*IJRER*) 12, no. 2 (2022): 768-798.

[37] Kang, Doho, Sarah Badawi, Zhituo Ni, Ahmed Abuelnaga, Mehdi Narimani, and Navid R. Zargari. "Review of Reduced Switch-Count Power Cells for Regenerative Cascaded H-Bridge Motor Drives." *IEEE Access (Aug 5, 2022).*

[38] Varesi, Kazem, Fatemeh Esmaeili, Saeid Deliri, and Hadi Tarzamni. "Single-Input Quadruple-Boosting Switched-Capacitor Nine-Level Inverter with Self-Balanced Capacitors." *IEEE Access 10 (2022): 70350-70361*.

[39] Hosseinzadeh, Mohammad Ali, Maryam Sarebanzadeh, Cristian Garcia, Ebrahim Babaei, Jose Rodriguez, and Ralph Kennel. "Reduced Multisource Switched-Capacitor Multilevel Inverter Topologies." *IEEE Transactions on Power Electronics (2022)*.

[40] Hosseinzadeh, Mohammad Ali, Maryam Sarebanzadeh, Cristian Garcia, Ebrahim Babaei, Jose Rodriguez, and Ralph Kennel. "Reduced Multisource Switched-Capacitor Multilevel Inverter Topologies." *IEEE Transactions on Power Electronics (2022)*.

[41] Liu, Junfeng, Jialei Wu, Jun Zeng, and Huafang Guo. "A novel nine-level inverter employing one voltage source and reduced components as high-frequency AC power source." *IEEE Transactions on Power Electronics 32, no. 4 (2016): 2939-2947.*

[42] Raman, S. Raghu, Ka Wai Eric Cheng, and Yuanmao Ye. "Multi-input switched-capacitor multilevel inverter for high-frequency AC power distribution." *IEEE Transactions on Power Electronics 33, no. 7 (2017): 5937-5948.*

[43] Sadigh, Arash Khoshkbar, Mostafa Abarzadeh, Keith A. Corzine, and Vahid Dargahi. "A new breed of optimized symmetrical and asymmetrical cascaded multilevel power converters." *IEEE Journal of Emerging and Selected Topics in Power Electronics 3, no. 4 (2015): 1160-1170.*

[44] Oskuee, Mohammad Reza Jannati, Masoumeh Karimi, Sajad Najafi Ravadanegh, and Gevork B. Gharehpetian. "An innovative scheme of symmetric multilevel voltage source inverter with lower number of circuit devices." *IEEE Transactions on Industrial Electronics* 62, no. 11 (2015): 6965-6973.

[45] Letha, Shimi Sudha, Tilak Thakur, and Jagdish Kumar. "Harmonic elimination of a photo-voltaic based cascaded H-bridge multilevel inverter using PSO (particle swarm optimization) for induction motor drive." *Energy 107 (2016): 335-346*.